Ayan Palchaudhuri Rajat Subhra Chakraborty

# High Performance Integer Arithmetic Circuit Design on FPGA

Architecture, Implementation and Design Automation

# **Springer Series in Advanced Microelectronics**

#### Volume 51

#### Series editors

Kukjin Chun, Seoul, Korea, Republic of (South Korea) Kiyoo Itoh, Tokyo, Japan Thomas H. Lee, Stanford, CA, USA Rino Micheloni, Vimercate (MB), Italy Takayasu Sakurai, Tokyo, Japan Willy M.C. Sansen, Leuven, Belgium Doris Schmitt-Landsiedel, München, Germany The Springer Series in Advanced Microelectronics provides systematic information on all the topics relevant for the design, processing, and manufacturing of microelectronic devices. The books, each prepared by leading researchers or engineers in their fields, cover the basic and advanced aspects of topics such as wafer processing, materials, device design, device technologies, circuit design, VLSI implementation, and subsystem technology. The series forms a bridge between physics and engineering and the volumes will appeal to practicing engineers as well as research scientists.

More information about this series at http://www.springer.com/series/4076

# High Performance Integer Arithmetic Circuit Design on FPGA

Architecture, Implementation and Design Automation

Ayan Palchaudhuri

Department of Electronics and Electrical

Communication Engineering

Indian Institute of Technology Kharagpur

Kharagpur, West Bengal

India

Rajat Subhra Chakraborty

Department of Computer Science

and Engineering

Indian Institute of Technology Kharagpur

Kharagpur, West Bengal

India

ISSN 1437-0387 ISSN 2197-6643 (electronic) Springer Series in Advanced Microelectronics ISBN 978-81-322-2519-5 ISBN 978-81-322-2520-1 (eBook) DOI 10.1007/978-81-322-2520-1

Library of Congress Control Number: 2015943832

Springer New Delhi Heidelberg New York Dordrecht London © Springer India 2016

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

Springer (India) Pvt. Ltd. is part of Springer Science+Business Media (www.springer.com)

To Ma, for her continuous prayers, support and inspiration.

Ayan Palchaudhuri

To Bunto, for her patience, love and understanding.

Rajat Subhra Chakraborty

#### **Preface**

Realization of high performance arithmetic circuits targeted towards a specific family of the high-end Field Programmable Gate Arrays (FPGAs) continue to remain a challenging problem. Many fast arithmetic circuits proposed over the decades may not be amenable to efficient realization on a selected FPGA architecture. Experience has shown that current CAD tools for FPGAs are often unable to infer the native architectural components efficiently from the given input Hardware Description Language (HDL) specification of the circuit, as they explore only a small design space close to the input architectural description. The logic synthesis techniques inherent to the CAD tools are also often unable to apply the proper Boolean identities and perform appropriate algebraic factoring and sub-expression sharing, especially when intermediate signals are tapped out or registered. Primitive instantiation is an effective approach for optimization of designs on the Xilinx FPGA platform, and is often simpler than rewriting the Register Transfer Level (RTL) code to coax the logic synthesis tool to infer the desired architectural components. In addition, the FPGA CAD tools often fail to achieve an efficient placement of logic blocks on the FPGA fabric, resulting in higher routing delays.

In this book, we describe the optimized implementations of several arithmetic datapath, controlpath, and pseudorandom sequence generator circuits. We explore regular, modular, cascadable, and bit-sliced architectures for these circuits, by directly instantiating the target FPGA-specific primitives in the HDL specifications of the circuits. We justify every proposed architecture with detailed mathematical analyses. We improve performance by enforcing a constrained placement of the circuit building blocks, by placing the logically related hardware primitives in close proximity to one another, thereby minimizing the routing delay. This is accomplished by supplying relevant placement constraints in the Xilinx proprietary "User Constraints File" (.ucf) format to the FPGA CAD tool.

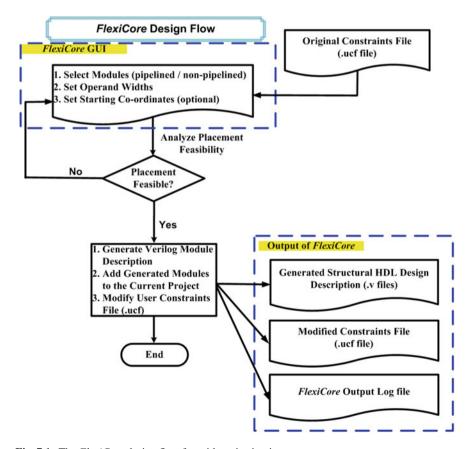

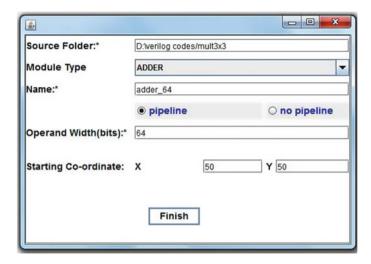

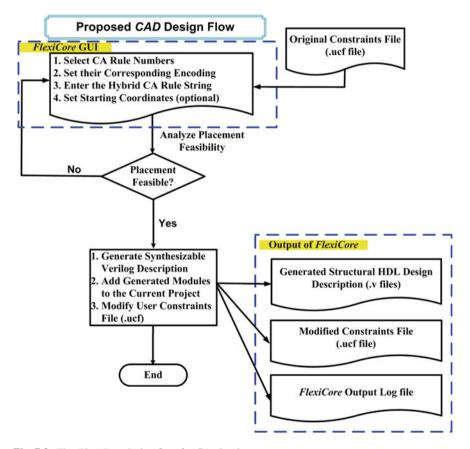

Taking advantage of the regularity of the architectures of the circuits proposed by us, the HDL specifications of the circuits as well as the placement constraints can be automatically generated. We have implemented a GUI-based CAD tool named *FlexiCore* integrated with the *Xilinx ISE* (Integrated Software Environment)

viii Preface

design environment for design automation of platform-specific high performance arithmetic circuits from user-level specifications. This tool was used to implement the proposed circuits, as well as hardware implementations of two integer arithmetic algorithms (Greatest Common Divisor (GCD) using Binary GCD algorithm and matrix multiplication using Distributed Arithmetic (DA)) where several of the proposed circuits were used as building blocks. Implementation results demonstrate higher performance and superior operand-width scalability at acceptable power-delay product (PDP) for the proposed circuits, with respect to implementations derived through other existing approaches.

Kharagpur

Ayan Palchaudhuri Rajat Subhra Chakraborty

## Acknowledgments

The authors thank Prof. Anindya Sundar Dhar, Department of Electronics and Electrical Communication Engineering, IIT Kharagpur, and Dr. Debdeep Mukhopadhyay, Department of Computer Science and Engineering, IIT Kharagpur, for their valuable insights into the work. The authors also acknowledge two undergraduate students of the Department of Computer Science and Engineering, IIT Kharagpur, Mohammad Salman and Sreemukh Kardas, for their contributions in developing the proposed CAD tool, *FlexiCore*.

This research was funded by a start-up research grant provided by IIT Kharagpur to Rajat Subhra Chakraborty.

# **Contents**

| 1 | Intr                                             | oduction                                               | 1  |  |  |  |  |

|---|--------------------------------------------------|--------------------------------------------------------|----|--|--|--|--|

|   | 1.1                                              | Background of FPGA-Based Design                        | 1  |  |  |  |  |

|   | 1.2                                              | Limitations of FPGA CAD Tools                          | 2  |  |  |  |  |

|   | 1.3                                              | Overview of Design Philosophy for FPGAs                | 3  |  |  |  |  |

|   |                                                  | 1.3.1 Target FPGA-Specific Hardware Primitive          |    |  |  |  |  |

|   |                                                  | Instantiation                                          | 3  |  |  |  |  |

|   | 1.4                                              | Existing FPGA CAD Tools                                | 4  |  |  |  |  |

|   |                                                  | 1.4.1 Xilinx IP Core Generator                         | 4  |  |  |  |  |

|   |                                                  | 1.4.2 <i>FloPoCo</i> (Floating-Point Cores)            | 5  |  |  |  |  |

|   | 1.5                                              | Recent Works on High Performance Circuit Realization   |    |  |  |  |  |

|   |                                                  | on Xilinx FPGAs                                        | 6  |  |  |  |  |

|   | 1.6                                              | Major Contributions of the Book                        | 6  |  |  |  |  |

|   | 1.7                                              | Organization of the Book                               | 8  |  |  |  |  |

|   | 1.8                                              | Summary                                                | 9  |  |  |  |  |

|   | References                                       |                                                        |    |  |  |  |  |

| 2 | Architecture of Target FPGA Platform             |                                                        |    |  |  |  |  |

|   | 2.1                                              | Introduction                                           | 11 |  |  |  |  |

|   | 2.2                                              | Fabric Slice Architecture for Virtex-5 FPGAs           | 12 |  |  |  |  |

|   | 2.3                                              | Fabric Slice Architecture for Virtex-6 FPGAs           | 14 |  |  |  |  |

|   | 2.4                                              | DSP Slice Architecture for Virtex-5 and Virtex-6 FPGAs | 15 |  |  |  |  |

|   | 2.5                                              | Implementation Overview                                | 16 |  |  |  |  |

|   | 2.6                                              | Summary                                                | 17 |  |  |  |  |

|   | Refe                                             | erences                                                | 17 |  |  |  |  |

| 3 | A Fabric Component Based Design Approach         |                                                        |    |  |  |  |  |

|   | for High-Performance Integer Arithmetic Circuits |                                                        |    |  |  |  |  |

|   | 3.1                                              | Introduction                                           | 19 |  |  |  |  |

|   | 3 2                                              | Existing Work                                          | 20 |  |  |  |  |

xii Contents

|   | 3.3                                  | Guide   | elines for High-Performance Realization               |  |  |  |  |  |

|---|--------------------------------------|---------|-------------------------------------------------------|--|--|--|--|--|

|   | 3.4                                  | Summ    | nary                                                  |  |  |  |  |  |

|   | Refe                                 | erences | 28                                                    |  |  |  |  |  |

|   |                                      |         |                                                       |  |  |  |  |  |

| 4 |                                      |         | re of Datapath Circuits                               |  |  |  |  |  |

|   | 4.1                                  |         | luction                                               |  |  |  |  |  |

|   | 4.2                                  | _       | er Adder/Subtractor Architecture                      |  |  |  |  |  |

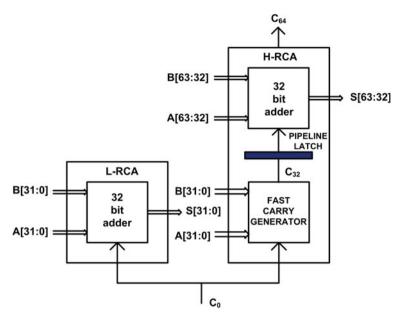

|   |                                      | 4.2.1   | Hybrid Ripple Carry Adder (Hybrid RCA)                |  |  |  |  |  |

|   |                                      | 4.2.2   | Xilinx DSP Slice-Based Adder                          |  |  |  |  |  |

|   |                                      | 4.2.3   | FloPoCo-Based Adder                                   |  |  |  |  |  |

|   |                                      | 4.2.4   | Fast Carry Adder Using Carry-Lookahead Mechanism 35   |  |  |  |  |  |

|   |                                      | 4.2.5   | Adder Implementation Results                          |  |  |  |  |  |

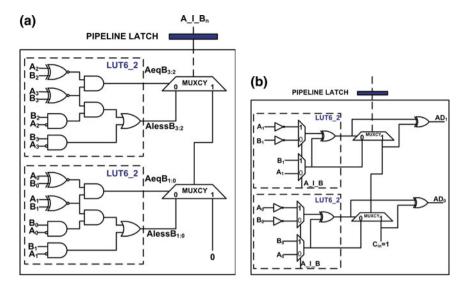

|   | 4.3                                  | Absol   | ute Difference Circuit Architecture 4.                |  |  |  |  |  |

|   |                                      | 4.3.1   | Proposed Absolute Difference Circuit                  |  |  |  |  |  |

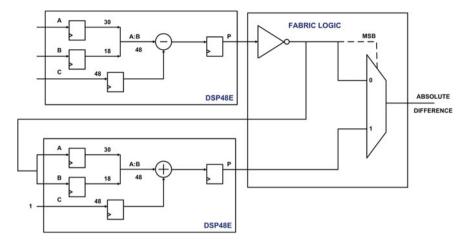

|   |                                      | 4.3.2   | DSP Slice-Based Absolute Difference Circuit 4         |  |  |  |  |  |

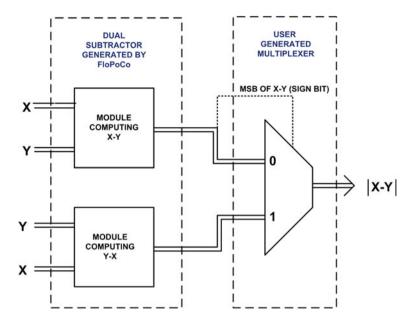

|   |                                      | 4.3.3   | FloPoCo-Based Absolute Difference Circuit 45          |  |  |  |  |  |

|   |                                      | 4.3.4   | Absolute Difference Circuit Implementation Results 40 |  |  |  |  |  |

|   | 4.4                                  | Intege  | er Multiplier Architecture                            |  |  |  |  |  |

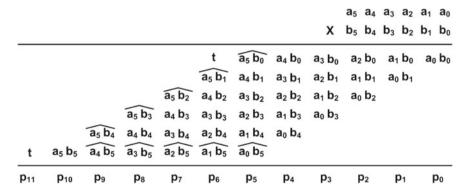

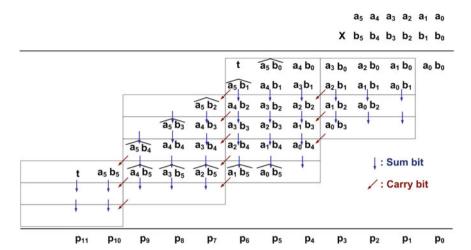

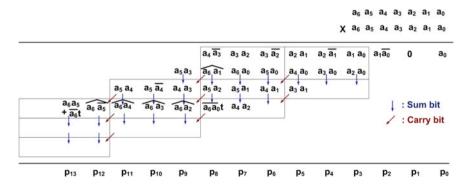

|   |                                      | 4.4.1   | Unsigned Integer Multiplier                           |  |  |  |  |  |

|   |                                      | 4.4.2   | Two's Complement Multiplier                           |  |  |  |  |  |

|   |                                      | 4.4.3   | Combined Unsigned and Two's Complement                |  |  |  |  |  |

|   |                                      |         | Multiplier                                            |  |  |  |  |  |

|   |                                      | 4.4.4   | DSP Slice-Based Signed Multiplier                     |  |  |  |  |  |

|   |                                      | 4.4.5   | FloPoCo-Based Signed Multiplier                       |  |  |  |  |  |

|   |                                      | 4.4.6   | Multiplier Implementation Results 55                  |  |  |  |  |  |

|   | 4.5                                  | Intege  | er Squarer Architecture 57                            |  |  |  |  |  |

|   |                                      | 4.5.1   | Unsigned Squarers                                     |  |  |  |  |  |

|   |                                      | 4.5.2   | Two's Complement Squarers                             |  |  |  |  |  |

|   |                                      | 4.5.3   | Combined Unsigned and Two's Complement Squarer 64     |  |  |  |  |  |

|   |                                      | 4.5.4   | DSP Slice-Based Squarers 65                           |  |  |  |  |  |

|   |                                      | 4.5.5   | FloPoCo-Based Squarers 6                              |  |  |  |  |  |

|   |                                      | 4.5.6   | Squarer Implementation Results 6                      |  |  |  |  |  |

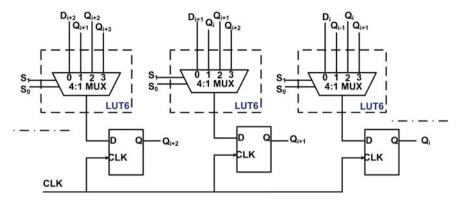

|   | 4.6                                  | Unive   | ersal Shift Register Architecture 6                   |  |  |  |  |  |

|   |                                      | 4.6.1   | Universal Shift Register 6                            |  |  |  |  |  |

|   |                                      | 4.6.2   | Universal Shift Register Implementation Results 69    |  |  |  |  |  |

|   | 4.7                                  | Summ    | nary 70                                               |  |  |  |  |  |

|   | Refe                                 | erences | 7                                                     |  |  |  |  |  |

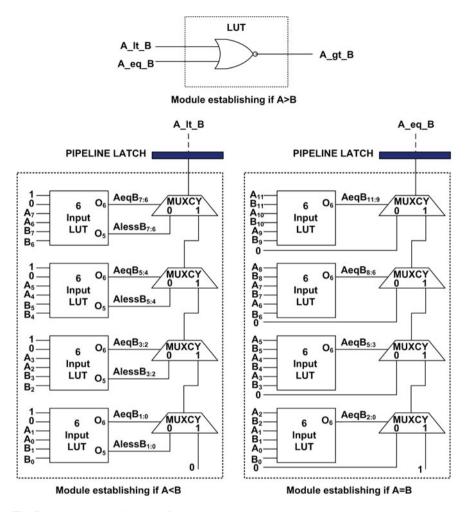

| 5 | Architecture of Controlpath Circuits |         |                                                       |  |  |  |  |  |

| J | 5.1                                  |         | re of Controlpath Circuits                            |  |  |  |  |  |

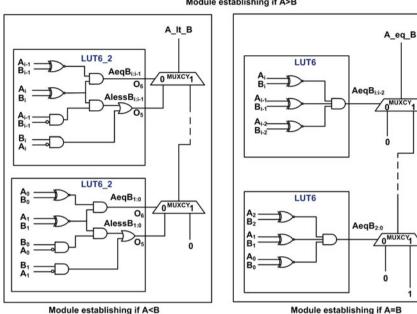

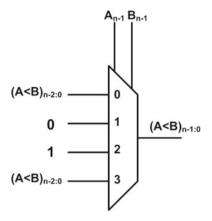

|   | 5.2                                  |         | er Comparator Architecture                            |  |  |  |  |  |

|   | ٥.۷                                  | 5.2.1   | Proposed Comparator Architecture                      |  |  |  |  |  |

|   |                                      | 5.2.2   | DSP Slice-Based Comparator                            |  |  |  |  |  |

|   |                                      |         | Comparator Implementation Results                     |  |  |  |  |  |

|   |                                      | -1-41   | - x x m m m m m m m m m m m m m m m m m               |  |  |  |  |  |

Contents xiii

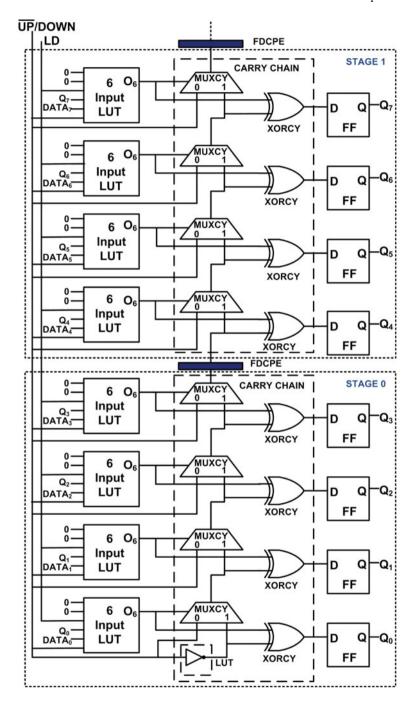

|    | 5.3                                                     | Loadable Bidirectional Binary Counter Architecture | 79  |  |  |  |  |

|----|---------------------------------------------------------|----------------------------------------------------|-----|--|--|--|--|

|    |                                                         | 5.3.1 Proposed Counter Architecture                | 79  |  |  |  |  |

|    |                                                         | 5.3.2 DSP Slice-Based Counter                      | 81  |  |  |  |  |

|    |                                                         | 5.3.3 Counter Implementation Results               | 81  |  |  |  |  |

|    | 5.4                                                     | Summary                                            | 82  |  |  |  |  |

|    | Refe                                                    | erences                                            | 83  |  |  |  |  |

| 6  | Compact FPGA Implementation of Linear Cellular Automata |                                                    |     |  |  |  |  |

|    | 6.1                                                     | Introduction                                       | 85  |  |  |  |  |

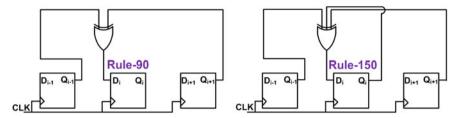

|    | 6.2                                                     | Preliminaries on Cellular Automata                 | 86  |  |  |  |  |

|    | 6.3                                                     | Adapting CA to the Native FPGA Architecture        | 88  |  |  |  |  |

|    | 6.4                                                     | CA Implementation Results                          | 89  |  |  |  |  |

|    | 6.5                                                     | Summary                                            | 90  |  |  |  |  |

|    | Refe                                                    | erences                                            | 91  |  |  |  |  |

| 7  | Design Automation and Case Studies                      |                                                    |     |  |  |  |  |

|    | 7.1                                                     | Introduction                                       | 93  |  |  |  |  |

|    | 7.2                                                     | The FlexiCore CAD Tool                             | 94  |  |  |  |  |

|    | 7.3                                                     | Case Studies                                       | 97  |  |  |  |  |

|    |                                                         | 7.3.1 GCD Calculator Circuit                       | 98  |  |  |  |  |

|    |                                                         | 7.3.2 Distributed Arithmetic-Based Matrix          |     |  |  |  |  |

|    |                                                         | Multiplication Circuit                             | 102 |  |  |  |  |

|    | 7.4                                                     | Summary                                            | 106 |  |  |  |  |

|    | Refe                                                    | erences                                            | 107 |  |  |  |  |

| 8  | Con                                                     | Conclusions and Future Work                        |     |  |  |  |  |

|    | 8.1                                                     | Introduction                                       | 109 |  |  |  |  |

|    | 8.2                                                     | Contributions of the Book                          | 109 |  |  |  |  |

|    | 8.3                                                     | Future Research Directions                         | 110 |  |  |  |  |

|    | Refe                                                    | erences                                            | 112 |  |  |  |  |

| In | dex .                                                   |                                                    | 113 |  |  |  |  |

## Acronyms

ASIC Application-Specific Integrated Circuit

BIST Built-In Self-Test CA Cellular Automata

CAA Cellular Automata Array

CAD Computer Aided Design

CDI Configuration Data In

CDO Configuration Data Out

CE Clock Enable

CL Combinational Logic CLB Configurable Logic Block

CORDIC COordinate Rotation DIgital Computer

DA Distributed Arithmetic

DFT Discrete Fourier Transform

DSP Digital Signal Processing

FloPoCo Floating-Point Cores

FF Flip-Flop

FFT Fast Fourier Transform FIR Finite Impulse Response

FPGA Field Programmable Gate Array

FSM Finite State Machine

GCD Greatest Common Divisor

GUI Graphical User Interface

HDL Hardware Description Language

HKMG High-K Metal Gate

HPL High Performance Low Power

IP Intellectual Property

ISE Integrated Software Environment LFSR Linear Feedback Shift Register LNS Logarithmic Number System

LUT Look-Up Table

MACC Multiply Accumulate

xvi Acronyms

MCNC Microelectronics Center of North Carolina

MISR Multiple-Input Signature Register

PDP Power-Delay Product PIPO Parallel-In Parallel-Out

PP Partial Product

RCA Ripple Carry Adder

RTL Register Transfer Level

SIMD Single Instruction Multiple Data

TCL Tool Command Language

TSMC Taiwan Semiconductor Manufacturing Company Limited

UCF User Constraints File

VHDL Very High Speed Integrated Circuit Hardware Description Language

XST Xilinx Synthesis Tool

#### **About the Authors**

Ayan Palchaudhuri is a Ph.D. student in the Department of Electronics and Electrical Communication Engineering (E&ECE) of Indian Institute of Technology (IIT) Kharagpur. He has received the M.S. degree from the Department of Computer Science and Engineering (CSE), IIT Kharagpur, in 2015. He has over 2.5 years of work experience as a Junior Project Assistant in the Department of CSE, IIT Kharagpur. His research interests include VLSI Architecture Design and Computer Arithmetic. He is the co-author of two conference papers, one journal, one book chapter, and a patent has been filed based on his research work. His research work has been recognized with the Best Poster Award in the Student Research Symposium of the 21st IEEE International Conference on High Performance Computing (HiPC) 2014.

Rajat Subhra Chakraborty is Assistant Professor in the Computer Science and Engineering Department of Indian Institute of Technology Kharagpur. He has a Ph.D. in Computer Engineering from Case Western Reserve University (Ohio, USA) and a B.E. (Hons.) in Electronics and Telecommunication Engineering from Jadavpur University (India) in 2005. He has work experience at National Semiconductor and AMD. His research interests include: Hardware Security, VLSI Design and Design Automation, and Reversible Watermarking for digital content protection. He is the co-author of two published books, four book chapters, and over 50 publications in international journals and conferences of repute. He is one of the recipients of the "IBM Faculty Award" for 2012, and a "Royal Academy of Engineering (UK) Fellowship" in 2014. He holds one U.S. patent, and two more international patents and three Indian patents have been filed based on his research work. Dr. Chakraborty is a member of IEEE and ACM.

# Chapter 1 Introduction

**Abstract** This chapter presents a concise overview of FPGA-based architecture design. Certain existing research work behind proposing new FPGA architectures and CAD heuristics to overcome the design limitations have been discussed. It also unfolds the limitations of the FPGA CAD tool that are currently popular for arithmetic core generation. A methodology that uses the target FPGA specific primitive instantiation-based approach and constrained placement exercise has been proposed as a superior alternative in comparison to design implementations available in literature. The major contributions of this book have also been listed.

#### 1.1 Background of FPGA-Based Design

Researchers over the years have proposed various Field Programmable Gate Array (FPGA) architectures for high performance realization of digital circuits, particularly those that have long cascading delay, e.g., ripple carry adder. In [19], an enhanced cascade circuit with dedicated routing structures for fast propagation of signals between cells was proposed to achieve a significant speedup. In [11], the authors had considered a folding method of logic functions and its adaptation to map to proposed Look-Up Table (LUT) architectures, such that the memory requirement for realization of the logic functions can be significantly reduced. It has also been studied that reducing the number of stages of programmable routing (e.g., routing through switchboxes) can significantly reduce the critical path [17]. This can be achieved through use of LUTs which support maximum functionality and dedicated routing along with other logic blocks. Experiments have confirmed that 6-input LUTs provide the right trade-off between critical path delay and design die size [3]. With culmination of all such similar research paradigms, modern FPGAs have architectural features amenable to the efficient implementation of combinational functions of arbitrary complexity in the form of LUTs, along with fast special-purpose logic and routing resources for propagating carry signals between adjacent logic blocks in form of *carry chain* [9].

However, with a significant increase in circuit complexity for FPGA-based designs, even the most sophisticated Computer Aided Design (CAD) tools often result in circuit implementations with unsatisfactory performance and resource

1

© Springer India 2016

A. Palchaudhuri and R.S. Chakraborty, *High Performance Integer Arithmetic Circuit Design on FPGA*, Springer Series in Advanced Microelectronics 51, DOI 10.1007/978-81-322-2520-1\_1

2 1 Introduction

requirements owing to their inability to optimally exploit the underlying FPGA architecture and their dedicated routing fabric. Hence, implementations derived through the standard automatic logic synthesis-based design flow starting with the behavioral Hardware Description Language (HDL) as the mode of design entry of the circuit, can be outperformed by more low-level "custom" design techniques. Extensive experimentation with the Xilinx FPGA CAD tool has shown that though the tool is able to infer the desired hardware primitives for many combinational logic circuits, it generally fails to do so when we synthesize sequential or pipelined architectures. In addition, the current FPGA CAD tools often fail to place the technology mapped sub-circuits at locations such that circuit delay is minimized. To overcome these limitations, a designer needs to identify the basic building blocks of the required circuit, and make an effort to optimally construct them from the hardware primitives available on the FPGA and ensure their proper placement. This book discusses several FPGA-specific design techniques that need to be adopted for optimal realization of high performance circuits and presents relevant case studies.

The rest of the chapter is organized as follows. In Sect. 1.2, we discuss the limitations of FPGA CAD tools for realization of high performance circuits. In Sect. 1.3, we describe the design philosophy that must be adopted to overcome the limitations posed by current FPGA CAD tools. Section 1.4 discusses two popular FPGA CAD tools—the standard *Xilinx Integrated Software Environment* (ISE)-based Graphical User Interface (GUI) for IP Core Generator and *FloPoCo* (in short for Floating–Point Cores) where user inputs circuit specifications and the CAD tool generates the corresponding synthesizable HDL specification of the circuit. In Sect. 1.5, we mention some of the recent works on architectural realization of arithmetic circuits on Xilinx FPGAs. We state the major contributions of this book in Sect. 1.6. The organization of the book is presented in Sect. 1.7.

#### 1.2 Limitations of FPGA CAD Tools

Modern CAD tools for FPGA platform facilitate the automatic mapping of binary addition logic to carry-chain structures to accelerate signal propagation, thereby achieving a speedup in the critical paths. In addition, existence of carry-chain simplifies routing by avoiding switch-boxes in the general routing fabric, and also increases the functional capability of the FPGA logic slices. Such benefits have been experimentally evaluated on the basis of combinational MCNC benchmarks in [15]. Though synthesis tools for Xilinx Virtex architectures are able to map the binary addition logic or a homogeneous wide AND and OR gates to *carry chain* fabric [16], or can infer the *wide function multiplexers* native to an FPGA slice, it fails to do so as soon as the final carry outputs of individual slices [14] or intermediate LUT outputs are tapped out or registered to facilitate pipelining of the architecture. A possible reason might be that Xilinx FPGA logic slices do not support dedicated hardware for registering such signals, and the CAD tools fail to infer the desired implementation. In such a scenario, the designer has to spell out special directives in the HDL of

the design or associated "constraints files" to the FPGA CAD tool, so that in the *packing* [1] or *clustering* step (as known in the FPGA CAD literature) of the FPGA design flow, the technology mapped circuit is efficiently "packed" into the available hardware resources.

#### 1.3 Overview of Design Philosophy for FPGAs

Most current FPGA vendors allow direct instantiation of the available primitives in the HDL code [21], and a "mixed" style of HDL coding, where high-level behavioral code is intermingled with relatively "low-level" structural code. Placement steps also need to be constrained and controlled, as the CAD placement tools, if allowed to perform unconstrained placement and routing, often result in large routing delays. This happens because the technology mapped logic elements get unevenly distributed across the FPGA fabric, resulting in greater routing and interconnect delays. This contributes to a major portion of the circuit critical path delay. Although most modern FPGA vendors provide special hardware IPs for common integer arithmetic operations which can be directly instantiated in the HDL code, we would demonstrate that we can do better by adopting careful design techniques.

To follow the methodology promoted above, the designer must possess a thorough understanding of the target FPGA architecture, the routing fabric, the available design elements in the form of primitives and macros, and how to configure them to achieve the required functionality. Also, the structure of the circuits must have sufficient regularity to automate their design, and to allow efficient placement and routing. Arithmetic circuits and Finite State Machines (FSMs) with regular structures (e.g., counters and shift registers) are thus the ideal candidates for this methodology.

#### 1.3.1 Target FPGA-Specific Hardware Primitive Instantiation

With sufficient modularity in the circuit architecture, it becomes easy to automate the generation of the HDL code, and associated constraint files which are themselves very regular in their grammar. Target FPGA-specific *primitive instantiation* is an effective approach for optimization of designs on the Xilinx FPGA platform [7], and is often the only approach. The primitive instantiation-based methodology is also simpler than rewriting the Register Transfer Level (RTL) code to coax the logic synthesis tool to infer the desired architectural components. However, in general, the entire circuit might not be amenable to the primitive instantiation-based design approach. In such cases, this approach can be adopted to design only those parts of the circuit that are amenable to such a methodology, and contribute significantly to the critical path delay. The only disadvantage of using such a design methodology is that the design becomes less portable, and becomes harder to maintain. In spite of this, the methodology is very effective in practice, considering the facts that (a) often

4 1 Introduction

the target FPGA platform is known before the circuit is designed and that (b) FPGAs from a related family from the same vendor are often backward compatible regarding the design elements (primitives and macros) supported. For example, newer versions of FPGAs of the "Virtex" family from Xilinx are expected to support primitives supported in some older Virtex versions. Thus, the HDL code for instantiating primitives targeting the older versions, and the constraints file to control the placement, can be reused in the newer version after small tweaks, if necessary. Added with the advantage of being able to automatically generate the circuit descriptions and the constraints, this is an attractive methodology.

#### 1.4 Existing FPGA CAD Tools

The most popular FPGA CAD tools for arithmetic core generation are the *Xilinx IP Core Generator* and an open source tool called *FloPoCo*. We briefly describe their main features and the relevant shortcomings.

#### 1.4.1 Xilinx IP Core Generator

The Xilinx IP Core Generator is part of the standard Xilinx ISE distribution, It includes a GUI-based utility, through which synthesizable HDL code (for common integer arithmetic circuits such as adders, multipliers, accumulators, counters, etc.) can be automatically generated. Designers can generate both combinational and pipelined versions of the arithmetic circuits, where the user enters the parameter latency as input for pipelined architecture realizations. Although such HDL automatically generated by the Xilinx software is functionally correct, it fails to give high performance when implemented, because the synthesis tool performs an inefficient technology mapping of the circuit, and the inferred logic elements are usually scattered in an apparently random fashion across the FPGA fabric, thereby causing large routing delays and affecting critical paths. Xilinx also allows the direct instantiation of "Digital Signal Processing" (DSP) hardware macros in the HDL targeted for FPGAs, which are highly customized dedicated arithmetic circuits. Individual Virtex-5 DSP slices can operate at a maximum frequency of 550 MHz [20], Virtex-6 DSP slices can operate at a maximum frequency of 600 MHz [22]; such operating frequencies are attainable at very low latency and are also suitable for low power applications. However, as we would demonstrate, they have performance limitations for large operand widths, and can be outperformed by the proposed circuits with aggressive pipelining, coupled with compact and constrained placement of logic primitives.

#### 1.4.2 FloPoCo (Floating-Point Cores)

FloPoCo is an open-source C++ framework for generating arithmetic cores for FPGAs [8]. FloPoCo provides a command-line interface through which the user can input operator specifications, and the program generates the corresponding synthesizable VHDL (Very High Speed Integrated Circuit Hardware Description Language) code. The main features of FloPoCo as listed in [6] are as follows:

- Supports integer, fixed point, floating point, and *Logarithmic Number System* (LNS) arithmetic.

- Supports pipelining by allowing the user to specify the desired operating frequency.

- Allows the user to specify the target FPGA implementation platform, and generates synthesizable VHDL code optimized for that target platform. In addition, FloPoCo performs target platform-specific pipelining, as its frequency-directed pipelining takes into consideration the timing information about the target FPGA platform [6]. FloPoCo comes with such models for the main FPGA families from both Xilinx and Altera.

However, detailed experimentation with the latest released version of *FloPoCo* (v 2.5.0) [8], and implementation and characterization of the integer arithmetic circuit descriptions generated by it indicate the following drawbacks:

- FloPoCo only generates pure behavioral VHDL code which cannot correctly infer the desired hardware primitives of the target FPGA platform. Consequently, it has no control over the inference and placement of logic blocks on the FPGA fabric. This makes the performance of the circuit post-synthesis worse than the target frequency specified by the user. Thus, FloPoCo provides no guarantee that the target frequency specified would be met in the final implementation.

- FloPoCo at times create very deep pipelines, apparently to meet input frequency constraints, but post place-and-route implementations do not guarantee that the delay constraints are met.

- Pipelining behavior of *FloPoCo* is very inconsistent. It was observed that for adder circuit implementations, *FloPoCo* creates very deep pipelines, whereas it creates fairly unbalanced and irregular pipelines for dual subtractor implementations, where each of the pipeline stages have different complexities. On the contrary, it completely avoids pipelining the integer multipliers, but, however, generates an erroneous comment in the VHDL code that it has achieved single stage pipelining. Similar observations have been made for the squarer circuits where *FloPoCo* is unable to pipeline squarer circuits whose input operand bit-widths are lower than 14, but create highly inefficient pipelines for squarer circuits of higher bit-widths. Our observations about these inconsistencies in the pipelining behavior of the current version of *FloPoCo* have been concurred with by the creators of *FloPoCo* through personal correspondence. They have acknowledged that a bug exists in their program, which they have filed and would probably be taken care of in future releases.

6 1 Introduction

Irrespective of the behavior of existing options for automatic generation of arithmetic circuit cores targeting FPGAs, the important approach to note is that most or all of them are agnostic of the "low–level" architecture of the target FPGA platform, and its routing issues. Consequently, they can be predicted to be unable to take advantage of the hardware primitives, and to generate the most optimal circuit descriptions for the target FPGA.

# 1.5 Recent Works on High Performance Circuit Realization on Xilinx FPGAs

In the recent literature, design of fast adders [18, 24] and absolute difference circuits [13] on the Xilinx Virtex-5 family of FPGAs have been reported. These works discuss the design of fast and efficient architectures by exploiting the *carry chain* and 6-input LUTs of the Virtex-5 family. In [2, 5], the authors have proposed methods to integrate DSP blocks along with fabric logic for realization of multiplier circuits. Similar approaches have been reported in [23] for realization of large integer squarers on FPGA. Researchers have also been proposing heuristics for efficient synthesis of FPGA-based circuits, notably on the class of circuits called "compressor trees" that generalizes multiperand addition, and the partial product reduction trees of parallel multipliers using carry-save arithmetic [12].

#### 1.6 Major Contributions of the Book

In this book, we explore the architecture of several high performance integer arithmetic circuits, built using primitive instantiation and constrained placement of targetspecific primitives on the Xilinx Virtex-5 and Virtex-6 FPGA fabric, and a CAD tool to automate their design. The architectures are essentially "bit-sliced", and conceived in a way such that the bit-slices can be directly mapped to hardware primitives available on the FPGA. In addition, the placement of the primitives is carefully constrained to improve the critical path delay, and throughput is increased further by appropriate pipelining [10]. We call the CAD tool FlexiCore, in short for "Flexible Arithmetic Soft **Core** Generator." It is flexible in a sense that the operand widths for the mapped circuits can be varied, and the CAD tool allows partial control to the user over the placement of the circuits on the FPGA fabric. The CAD tool is integrated into the standard Xilinx ISE design environment, thus making it extremely convenient to a large user community, although nothing prevents our CAD tool (with minor modifications) to be part of other FPGA CAD frameworks. The circuits currently supported by the CAD tool are the ones most widely used in the domains of integer arithmetic algorithms, digital signal processing, and digital image processing. The use of the tool can also be easily extended for Xilinx FPGA platforms other than Virtex-5, after taking care of small modifications (e.g., changes in the "library primitive" names supported by Xilinx).

To summarize, the following are the main contributions of our work:

- We develop a methodology to design high performance widely used integer arithmetic circuits and pseudorandom binary sequence generators for Xilinx Virtex-5 and Virtex-6 FPGAs, while utilizing optimum hardware resources and having acceptable power-delay product (PDP) wherever possible. The main insight is to make optimal use of certain hardware primitives of the target FPGA platform, and constrained placement of the primitives, combined with pipelining (as required).

- We elaborate on certain useful observations which act as important guidelines for compact and high-performance realization of circuits realized using fabric logic on modern high-end FPGAs from Xilinx. These involve manipulation of the Boolean logic equations a priori in the HDL circuit descriptions, to forms that can be optimally mapped to the native target architecture by the CAD software.

- We adopt a bit-sliced design paradigm where an entire arithmetic circuit is built using identical modules of smaller bit width. As the stages of the building blocks are identical, it is easier to perform an optimal, fine-grained, and forward path pipelining. For some (two) circuits, we optimize the performance of the implementations derived using previously proposed architectures, while for the other circuits, we develop the architectures from first principles. In all cases, we provide in detail the Boolean logic-based mathematical analyses and proofs of correctness leading to the architectures, at times supplementing the analyses presented in the original sources of the architectures.

- The designs generated by our CAD framework show better operand-width scalability in comparison to previously proposed designs [24], i.e., lesser decrease of performance with the increase in operand width. However, any performance (speed) deterioration observed with increase in operand width is mainly attributed to the geometry of the FPGA devices and certain complex routing issues (either due to the fabric architecture or due to the complex digital logic circuitry), both of which are practically unavoidable by the user.

- Our designs outperform the circuits built using the GUI-based circuit generator utility in-built in *Xilinx ISE*, or by using the DSP slice hard macros, or the arithmetic cores generated by *FloPoCo*.

- Our CAD tool is integrated in the *Xilinx ISE* design environment to automate the design of the circuits, including automatic generation of the necessary placement constraint files.

- We demonstrate the effectiveness of the proposed design methodology by the complete "bottom-up" design of a 32-bit Greatest Common Divisor (GCD) calculation circuit, and a Distributed Arithmetic (DA)-based Matrix Multiplication circuit that utilizes several circuit building blocks generated by our CAD utility.

To the best of our knowledge, custom level implementation of logic elements on FPGA fabric for obtaining superior speed performances has not been extensively studied or reported in research articles. The previous literature reports high level HDL modeling for FPGA-based arithmetic circuit design [4], however, our design

8 1 Introduction

philosophy for FPGAs is slightly different in nature, as would be revealed in more detail in the upcoming chapters. This book aims to address this design philosophy and validate the entire exercise by presenting suitable examples and case studies.

#### 1.7 Organization of the Book

- Chapter 1 is the introductory chapter which discusses some of the existing work behind proposing new FPGA architectures, mapping of logic functions into proposed LUT architectures, along with limitations of the CAD algorithms for optimized mapping of logic into the FPGA fabric. It also presents the modern-day FPGA architectural components available in the high-end FPGA families coming from Xilinx. The existing Xilinx FPGA CAD tools available to designers and their limitations have been mentioned. A methodology to overcome these limitations using the art of primitive instantiation and constrained placement exercise has been proposed.

- Chapter 2 provides architectural details for the Virtex-5 and Virtex-6 FPGA platforms. It also discusses the different modes of implementations that *Xilinx ISE* provides to generate arithmetic circuit descriptions.

- Chapter 3 provides the fabric component-based approach for design of high performance integer arithmetic circuits for FPGAs. The Boolean logic manipulation and restructuring involved to map circuits optimally into the available FPGA hardware primitives has been presented.

- Chapter 4 presents the pipelined implementations of common arithmetic datapath circuits such as integer adder, absolute difference circuit, combined unsigned

and two's complement integer multiplier and squarer, and universal shift register.

We also present their Boolean logic-based mathematical analyses, proofs of correctness, and the post place-and-route implementation results clearly reveal the

superiority and advantages of our proposed design philosophy.

- Chapter 5 presents the pipelined implementations of arithmetic controlpath circuits such as integer comparator and loadable bidirectional counter along with their Boolean logic-based mathematical analyses, and the post place-and-route implementation results. Once again, the results clearly reveal the superiority and advantages of our proposed design philosophy.

- Chapter 6 discusses the FPGA-based implementation of cellular automata (CA)-based pseudorandom binary sequence generator.

- Chapter 7 introduces the CAD tool for design automation, *FlexiCore*, for automating the HDL of arithmetic circuits along with the placement constraint related files developed by us. The CAD tool can support the generation of multiple module-based designs which has been put to use for the design of a Greatest Common Divisor (GCD) circuit and a Distributed Arithmetic (DA)-based matrix multiplication circuit. The superior performance of the designs whose descriptions have been generated by *FlexiCore* have been tabulated.

- Chapter 8 summarizes the contributions and draws the future research directions.

1.8 Summary 9

#### 1.8 Summary

In this chapter, we have presented a concise overview of the limitations of the existing CAD tools for FPGA realization regarding optimal synthesis, technology mapping, and placement for realization of high performance arithmetic pipelined blocks. The overview of the design philosophy adopted by us for FPGA realization of arithmetic circuits has been provided with some recent works on high performance FPGA-based arithmetic circuit design. We have also spelt out the major contributions of the book. In the next chapter, we will discuss the architecture of the building blocks of our target FPGA platform.

#### References

- Ahmed, T., Kundarewich, P.D., Anderson, J.H.: Packing techniques for virtex-5 FPGAs. ACM Trans. Reconfig. Technol. Syst. (TRETS). 2(18), 18:1–18:24 (2009)

- Athow, J.L., Al-Khalili, A.J.: Implementation of large-integer hardware multiplier in Xilinx FPGA. In: 15th IEEE International Conference on Electronics, Circuits and Systems (ICECS), pp. 1300–1303 (2008)

- 3. Cosoroaba, A., Rivoallon, F.: Xilinx Inc., White Paper: Virtex-5 Family of FPGAs, Achieving Higher System Performance with the Virtex-5 Family of FPGAs, WP245 (v1.1.1). http://www.xilinx.com/support/documentation/white\_papers/wp245.pdf. Cited 7 July 2006

- 4. Deschamps, J.-P., Sutter, G.D., Canto, E.: Guide to FPGA Implementation of Arithmetic Functions. Ser. Lecture Notes in Electrical Engineering. Springer, vol. 149 (2012)

- 5. de Dinechin, F., Pasca, B.: Large Multipliers With Fewer DSP Blocks. In: International Conference on Field Programmable Logic and Applications (FPL), pp. 250–255 (2009)

- de Dinechin, F., Pasca, B.: Designing custom arithmetic data paths with FloPoCo. IEEE Des. Test Comput. 28(3), 18–27 (2011)

- 7. Ehliar, A.: Optimizing Xilinx designs through primitive instantiation. In: Proceedings of the 7th FPGAworld Conference, pp. 20–27 (2010)

- 8. FloPoCo.: Arithmetic Core Generator. http://flopoco.gforge.inria.fr/. Cited 12 Sep 2013

- 9. Hauck, S., Hosler, M.M., Fry, T.W.: High-Performance Carry Chains for FPGA's. In: IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 8(2), 138–147 (2000)

- Jump, J.R., Ahuja, S.R.: Effective pipelining of digital systems. IEEE Trans. Comput. 27(9), 855–865 (1978)

- Kimura, S., Horiyama, T., Nakanishi, M., Kajihara, H.: Folding of logic functions and its application to look up table compaction. In: IEEE/ACM International Conference on Computer Aided Design (ICCAD), pp. 694–697 (2002)

- 12. Parandeh-Afshar, H., Neogy, A., Brisk, P., Ienne, P.: Compressor Tree Synthesis on Commercial High-Performance FPGAs. ACM TRETS. **4**(4), 39:1–39:19 (2011)

- 13. Perri, S., Zicari, P., Corsonello, P.: Efficient absolute difference circuits in Virtex-5 FPGAs. In: 15th IEEE Mediterranean Electrotechnical Conference (MELECON), pp. 309–313 (2010)

- Preuβer, T.B., Spallek, R.G.: Mapping basic prefix computations to fast carry-chain structures.

In: International Conference on Field Programmable Logic and Applications (FPL), pp. 604–608 (2009)

- Preuβer, T.B., Spallek, R.G.: Enhancing FPGA device capabilities by the automatic logic mapping to additive carry chain. In: International Conference on Field Programmable Logic and Applications (FPL), pp. 318–325 (2010)

- Preuβer, T.B., Zabel, M., Spallek, R.G.: Accelerating computations on FPGA carry chains by operand compaction. In: 20th IEEE Symposium on Computer Arithmetic (ARITH), pp. 95–102 (2011)

10 1 Introduction

17. Singh, S., Rose, J., Chow, P., Lewis, D.: The effect of logic block architecture on FPGA performance. IEEE J. Solid-State Circ. 27(3), 281–287 (1992)

- Vazquez, M., Sutter, G., Bioul, G., Deschamps, J.P.: Decimal adders/subtractors in FPGA: Efficient 6-input LUT implementations. In: International Conference on Reconfigurable Computing and FPGAs (ReConFig), pp. 42–47 (2009)

- Woo, N.-S.: Revisiting the cascade circuit in logic cells of lookup table based FPGAs. In: Proceedings of the Third International ACM Symposium on Field-Programmable Gate Arrays, pp. 90–96 (1995)

- 20. Xilinx Inc.: Virtex-5 FPGA XtremeDSP Design Considerations User Guide, UG193 (v3.5). http://www.xilinx.com/support/documentation/user\_guides/ug193.pdf. Cited 26 Jan 2012

- 21. Xilinx Inc.: Virtex-5 Libraries Guide for HDL Design, UG621 (v11.3). http://www.xilinx.com/support/documentation/sw\_manuals/xilinx11/virtex5\_hdl.pdf. Cited 6 Sep 2009

- Xilinx Inc.: Virtex-6 FPGA DSP48E1 Slice User Guide, UG369 (v1.3). http://www.xilinx. com/support/documentation/user\_guides/ug369.pdf. Cited 14 Feb 2011

- 23. Xu, S., Fahmy, S.A., McLoughlin I.V.: Efficient large integer squarers on FPGA. In: 21st Annual International IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM), pp. 198–201 (2013)

- 24. Zicari, P., Perri, S.: A fast carry chain adder for Virtex-5 FPGAs. In: 15th IEEE Mediterranean Electrotechnical Conference (MELECON), pp. 304–308 (2010)

## Chapter 2 **Architecture of Target FPGA Platform**

**Abstract** This chapter provides an insight into the architecture of Configurable Logic Blocks (CLBs), the basic building blocks of a FPGA, including details of the Look-Up Tables, wide function multiplexers, carry chains, flip-flops, and DSP slices. It also gives an overview of the different modes of implementation supported by Xilinx ISE to realize arithmetic functions.

#### 2.1 Introduction

Current FPGAs such as the advanced Virtex and Spartan families of Xilinx FPGAs (e.g., Virtex-5, Virtex-6 and Spartan-6), promise immense hardware logic support, at higher integration, lower power consumption, and maximum performance. Maximum system performance requires a balanced mix of performance-efficient FPGA components: logic fabric (Look-Up Tables (LUTs), special functions like carry chains and dedicated multiplexers, flip-flops (FFs)), on-chip RAM, DSP blocks, and I/Os. Virtex-5 FPGAs have been the first FPGA device fabricated at the 65 nm CMOS technology node. Switching from 90 nm (for Virtex-4 FPGAs) to 65 nm (for Virtex-5 FPGAs) [4] have promised the above-mentioned advantages. Spartan-6 FPGAs, on the other hand, are built on a mature 45 nm low-power copper process technology [3] that delivers the optimal balance of cost, power and performance, whereas Virtex-6 FPGAs are built using a 40 nm state-of-the-art copper process technology, and are a programmable alternative to custom ASIC technology [9]. Xilinx 7 series FPGAs leverage the unprecedented power, performance, and capacity enabled by TSMC's (Taiwan Semiconductor Manufacturing Company Limited) 28 nm [2] high-k metal gate (HKMG), high performance, low power (HPL) process technology, and the unparalleled scalability afforded by the FPGA industry's first scalable, optimized architecture to provide a comprehensive platform base for next-generation systems.

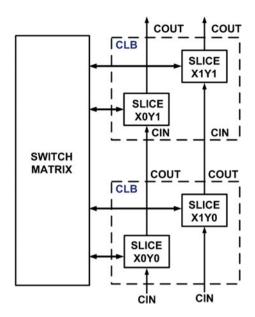

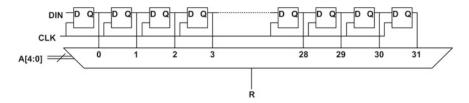

The Configurable Logic Blocks (CLBs) of FPGAs are the main logic resources for implementing sequential as well as combinatorial circuits. Each CLB element is connected to a switch matrix for access to the general routing matrix as shown in Fig. 2.1. Each CLB element for Virtex-5 and Virtex-6 series of FPGAs (that have been our target platform for implementation) contain a pair of slices. These two slices do not have direct connections to each other, and each slice is organized as a column.

**Fig. 2.1** Arrangement of slices within the CLB [5]

The Xilinx tools designate slices with the following definitions [5]. An "X" followed by a number identifies the position of each slice in a pair as well as the column position of the slice. A "Y" followed by a number identifies a row of slices. The number remains the same within a CLB, but counts up in sequence from one CLB row to the next CLB row.

The rest of the chapter is organized as follows. In Sect. 2.2, we present the slice architecture for Xilinx Virtex-5 FPGAs. In Sect. 2.3, we present the additional and modified features that Virtex-6 FPGAs offer in comparison to Virtex-5 FPGAs. A brief overview of the DSP slice architecture has been presented in Sect. 2.4. The different modes of implementation—fabric and DSP slice logic have been discussed in Sect. 2.5. We conclude in Sect. 2.6.

#### 2.2 Fabric Slice Architecture for Virtex-5 FPGAs

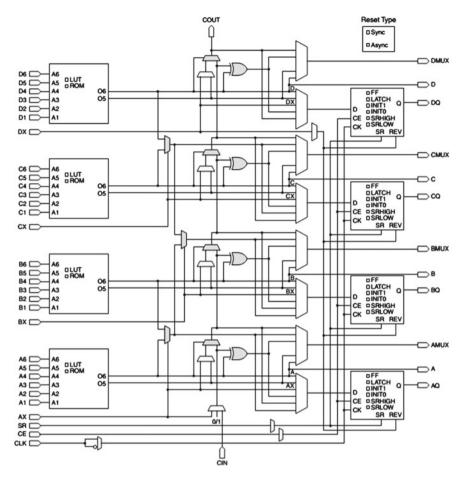

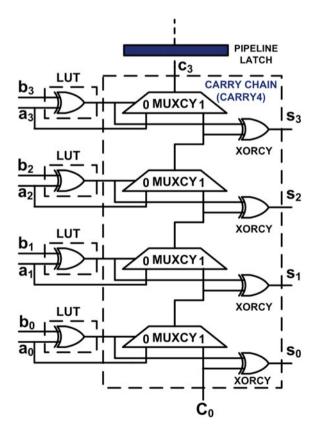

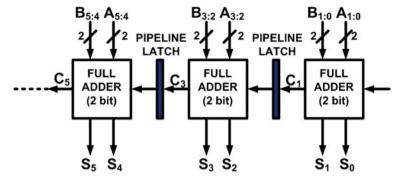

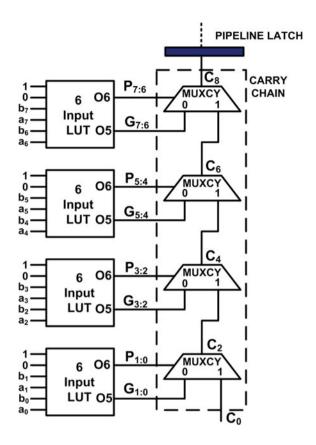

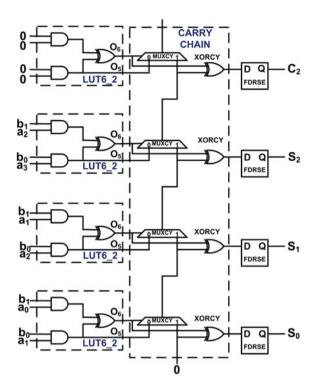

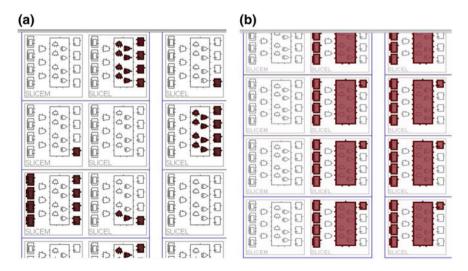

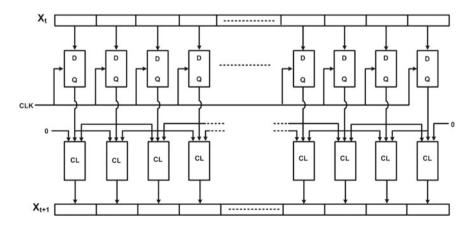

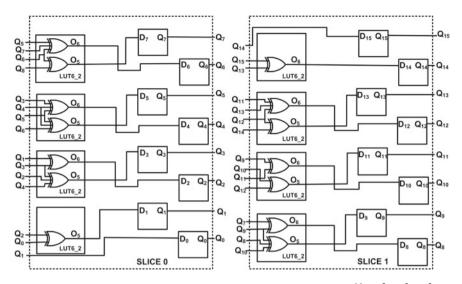

The CLBs of Xilinx FPGA are the main logic resources for implementing combinational and sequential circuits. A typical CLB of Virtex-5 FPGA contains 2 "slices," with each slice (called a "SLICEL" or "SLICEM" in Xilinx terminology depending on the nature of LUTs) comprising of four 6-input logic-function generators or LUTs, four storage elements or FFs, three wide function multiplexers, and a length-4 carry chain comprising of multiplexers and XOR gates [1, 5] as shown in Fig. 2.2. All these elements are used by the slices for realization of arithmetic, logic, and memory functions.

Fig. 2.2 Xilinx Virtex-5 slice architecture [5]

The Xilinx Virtex-5 family has been the first FPGA platform to offer a true 6-input LUT, with fully independent (not shared) inputs. This allows the implementation of functions with higher operand width and reduces the number of logic levels between registers. The 6-input LUT can also be configured as a 5 (or less) input, 2-output logic function with shared inputs, thereby reducing the requirement in the number of LUTs from two to one for certain logic expressions elaborated in Chap. 3. The LUTs present in SLICEL can implement any arbitrary combinational logic, whereas the LUTs in SLICEM can be implemented as a synchronous RAM resource called a distributed RAM element. The carry chain represents the fast carry propagation logic and the LUTs in the slice can be optionally connected to the carry chain via dedicated routes to implement complex logic functionality [7]. The storage elements in a slice can be configured as either edge-triggered D-type FFs or level-sensitive latches. Each FF can be controlled using the control signals *set*, *reset*, *clock*, and *clock enable* signals.

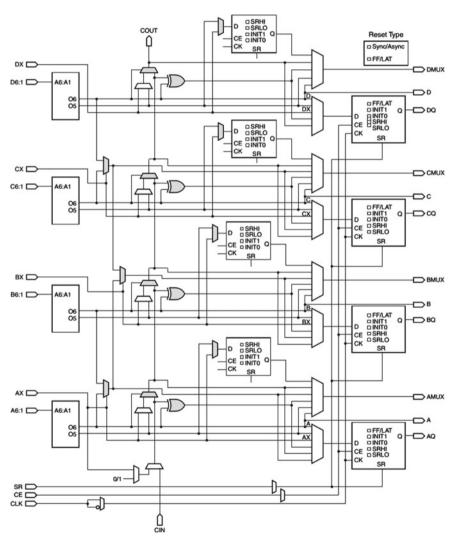

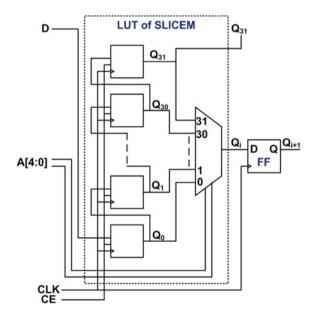

#### 2.3 Fabric Slice Architecture for Virtex-6 FPGAs

Virtex-6 slice architecture is quite similar to Virtex-5 slice architecture, other than the fact that it offers four additional storage elements in every slice in comparison to Virtex-5 to facilitate more efficient pipelining and improved routing. However, every storage element has one control signal less, i.e., it does not have independent set and reset pins, as compared to Virtex-5 architecture. The slice architecture for Virtex-6 FPGAs is shown in Fig. 2.3. Other than that, it supports a higher bandwidth with

Fig. 2.3 Xilinx Virtex-6 slice architecture [8]

greater number of serial transceivers that can deliver at a higher Gbps rate, along with a faster global clocking with lower skew, improved jitter and faster clock trees in comparison to Virtex-5 FPGA platforms.

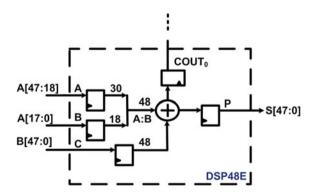

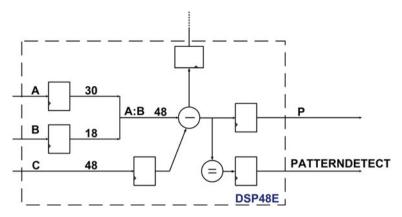

#### 2.4 DSP Slice Architecture for Virtex-5 and Virtex-6 FPGAs

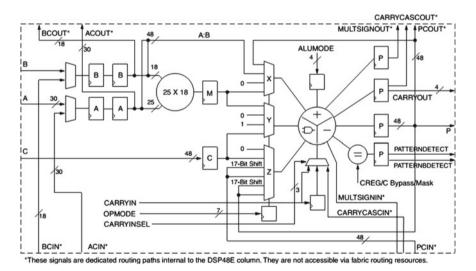

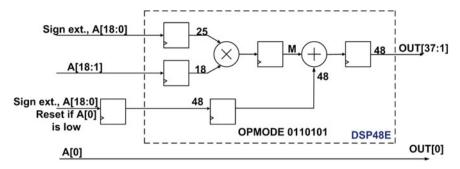

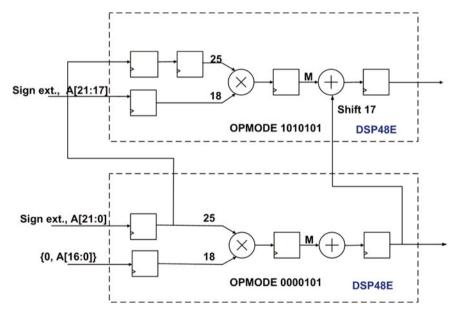

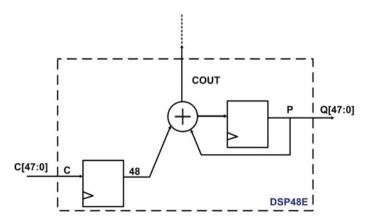

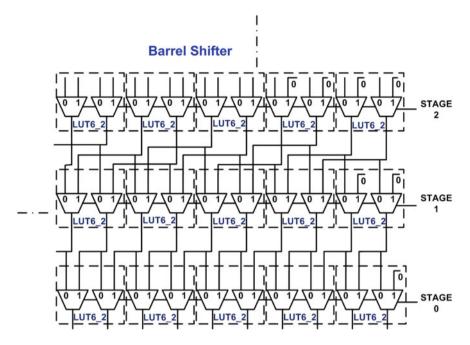

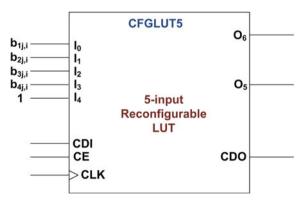

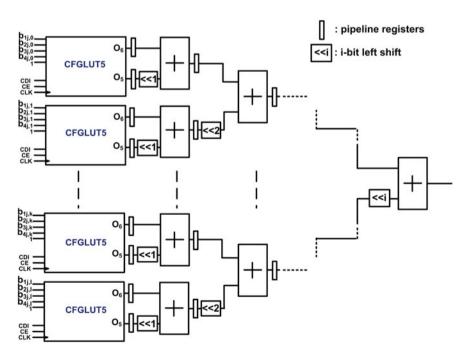

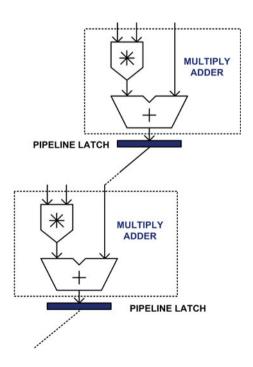

DSP slices in FPGAs are typically designed for low power applications as it significantly avoids fabric routing, but provides a reasonable speed of operation. The Virtex-5 FPGA DSP48E slice, as shown in Fig. 2.4, supports several independent arithmetic functionalities. Such functional units include a  $25 \times 18$  two's complement multiplier, multiply accumulate (MACC) unit, multiply adder, three-input adder, barrel shifter, wide-bus multiplexer, magnitude comparator, bitwise logic functions, pattern detector, and wide counter. The slice has internal pipeline stages which must be used for achieving maximum performance up to  $550\,\mathrm{MHz}$ .

For Virtex-6 FPGAs, the DSP slice available, DSP48E1, has all the features of a Virtex-5 FPGA DSP48E slice with certain additional features [10]. When all pipeline stages are used, Virtex-6 DSP slices can achieve a 600 MHz speed of operation. It supports an additional 25-bit pre-adder and register with another additional control unit.

Fig. 2.4 Xilinx Virtex-5 DSP48E slice [6]

#### 2.5 Implementation Overview

Native platform-dependent primitives such as 6-input LUT and carry chain can be directly instantiated in the HDL circuit description, and they appear unchanged in the final implementation mapped on the FPGA. For efficient and high performance design, the designer must ensure maximum utilization of the logic elements within each slice, and place the logically related slices into adjacent locations.

Designs targeted toward Virtex-5 and Virtex-6 FPGAs can also exploit IP cores available specifically for various arithmetic and logic functions. The Xilinx *Logi-CORE*® hard IP provides two modes of implementation: *Fabric* and *XtremeDSP*®. Fabric implementation involves utilization of LUTs, FFs, multiplexers and carry chains, whereas *XtremeDSP* implementation involves utilization of the special *DSP* slice which can also be instantiated as a primitive. DSP slice-based implementations guarantee lower power consumption in comparison to fabric logic, but as we would find, cannot always match the performance achievable by circuits implemented using constrained placement of Xilinx fabric logic.

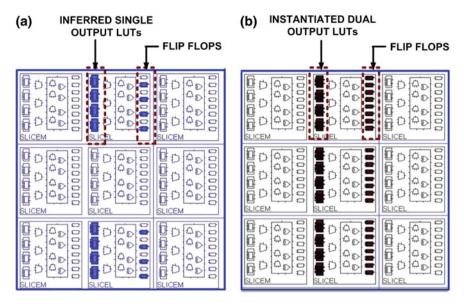

Most of our performance results have been reported using the Virtex-5 FPGA as the implementation platform. However, for certain circuits, like the cellular automata-based pseudorandom binary sequence generator or the matrix multiplication circuit, where it is necessary to register the dual outputs of the LUTs, Virtex-6 have been chosen as the implementation platform to ensure a compact implementation and pack more registers into a single slice, thereby freeing up resources that would otherwise have spanned across multiple slices and depleted adjacent slices of their register resources.

The circuits described in Chap. 4–7 were implemented either on a Xilinx Virtex-5 FPGA, device family XC5VLX330T, package FF1738 and speed grade -2 or Xilinx Virtex-6 FPGA, device family XC6VLX550T, package FF1760 and speed grade -2 using the Xilinx ISE 12.4 design environment. The speed of operation, resource utilization, and power–delay product (PDP) of the architectures have been compared with those reported in existing literature (if any) and with different modes of implementation have been tabulated. The designs have been evaluated in terms of speed, resource consumption in terms of FFs, LUTs, slices and DSP hard macros (whenever applicable), and power–delay product (PDP). Power–delay product has been calculated as the product of the power dissipation (sum of clock, logic, signal, and DSP power dissipation), the (minimum) clock-period (toggle rate of 12.5%), and the latency (in terms of the number of clock cycles required to complete the computation).

Functions implemented using the DSP slices consume less power than those implemented in general FPGA fabric [6], and this would be evident from the results. However, it would also be evident that the proposed methodology based on fabric logic, combined with careful and constrained placement can outperform the DSP slice-based design with respect to speed. To achieve maximum performance using the DSP slices, it is desirable to use all the pipeline stages within the DSP slice.

2.6 Summary 17

#### 2.6 Summary

In this chapter, we have introduced the modern and advanced families of Xilinx FPGAs that provide immense logic integration facilities and architectural support for high-performance implementations. The slice architectures for Virtex-5 and Virtex-6 FPGA families were described. An overview of the different modes of implementation were presented.

The next chapter will address a fabric component-based approach for realization of arithmetic circuits on modern FPGA families, where certain guidelines for manipulation and decomposition of Boolean logic level equations describing the implemented circuits will be discussed so that they can be easily and efficiently mapped to the physical fabric logic primitives of the target FPGA platform. Such an approach also allows the designer to predict the overall hardware cost and ensure a careful and compact placement of the logic architectures on the FPGA fabric. Certain examples of useful and practical circuits have also been described to illustrate the application of such guidelines for logic design.

#### References

- 1. Cosoroaba, A., Rivoallon, F.: Xilinx Inc., White Paper: Virtex-5 Family of FPGAs, Achieving Higher System Performance with the Virtex-5 Family of FPGAs, WP245 (v1.1.1). http://www.xilinx.com/support/documentation/white\_papers/wp245.pdf. Cited 7 July 2006

- Mehta, N.: Xilinx Inc., Xilinx 7 series FPGAs: the logical advantage, WP405 (v1.0). http://www.xilinx.com/support/documentation/white\_papers/wp405-7Series-Logical-Advantage.pdf. Cited 6 Mar 2012

- 3. Xilinx Inc.: Spartan-6 family overview, DS160 (v2.0). http://www.xilinx.com/support/documentation/data\_sheets/ds160.pdf. Cited 25 Oct 2011

- Xilinx Inc.: Virtex-5 family overview, DS100 (v5.0). http://www.xilinx.com/support/documentation/data\_sheets/ds100.pdf. Cited 6 Feb 2009

- Xilinx Inc.: Virtex-5 FPGA user guide, UG190 (v5.4). http://www.xilinx.com/support/documentation/user\_guides/ug190.pdf. Cited 16 Mar 2012

- Xilinx Inc.: Virtex-5 FPGA xtremeDSP design considerations user guide, UG193 (v3.5). http://www.xilinx.com/support/documentation/user\_guides/ug193.pdf. Cited 26 Jan 2012

- Xilinx Inc.: Virtex-5 libraries guide for HDL designs, UG621 (v11.3). http://www.xilinx.com/support/documentation/sw\_manuals/xilinx11/virtex5\_hdl.pdf. Cited 6 Sep 2009

- 8. Xilinx Inc.: Virtex-6 FPGA configurable logic block, UG364 (v1.2). http://www.xilinx.com/support/documentation/user\_guides/ug364.pdf. Cited 3 Feb 2012

- Xilinx Inc.: Virtex-6 family overview, DS150 (v2.4). http://www.xilinx.com/support/documentation/data\_sheets/ds150.pdf. Cited 19 Jan 2012

- Xilinx Inc.: Virtex-6 FPGA DSP48E1 slice user guide, UG369 (v1.3). http://www.xilinx.com/support/documentation/user\_guides/ug369.pdf. Cited 14 Feb 2011

# Chapter 3 A Fabric Component Based Design Approach for High-Performance Integer Arithmetic Circuits

**Abstract** This chapter elaborates on some useful guidelines that can be helpful for compact and high-performance realization of circuits on modern high-end FPGAs from Xilinx. It involves manipulation of the Boolean equations *a priori* in the HDL circuit descriptions to forms that can be optimally mapped to the native target architecture by the CAD software. Although the guidelines are relatively simple, they are extremely useful in the efficient realization of numerous arithmetic circuits which can be constructed using the "bit-sliced" design paradigm.

#### 3.1 Introduction

Implementation of highly optimized arithmetic circuits targeted toward a specific family of high-end FPGAs continue to remain a challenging problem. This is because the architecture of many fast arithmetic circuits that have been proposed over the decades may not be amenable to a much optimized implementation for a selected FPGA. Also, often the logic synthesis CAD software tools are unable to infer the desired native building-block components from the given input HDL specification of the circuit, as they explore only a small design space close to the input architectural description [5]. In addition, the logic synthesis algorithms used internally by the CAD tools are unable to apply the logic identities and perform appropriate algebraic factoring and subexpression sharing in many cases, especially when intermediate signals are tapped out [3] or registered to facilitate pipelining of the architecture.

It is in general a nontrivial computational problem to decompose the Boolean equations describing the implemented circuit, to forms such that the resultant subexpressions can be mapped easily and efficiently to the physical primitives of the fabric logic on the target FPGA. It helps if the designer manipulates the Boolean equations *a priori* in the HDL circuit descriptions, to forms that can be optimally mapped to the native target architecture by the CAD software.

The rest of the chapter is organized as follows. In Sect. 3.2, we discuss an existing work that estimates the hardware cost to map a Boolean function of x variables using k-input LUTs. We also discuss certain limitations behind the philosophy of making

such an estimate. In Sect. 3.3, we elaborate on certain important guidelines for high-performance realization of circuits on modern high-end FPGAs from Xilinx. We conclude in Sect. 3.4.

#### 3.2 Existing Work

A previous work [4] had reported area requirements (for LUT-based FPGAs) in terms of the total number of *k*-input LUTs required to map a function of *x* variables, as

$$lut(x) = \begin{cases} 0 & \text{if } x \le 1\\ 1 & \text{if } 1 < x \le k\\ \lfloor \frac{x-k}{k-1} \rfloor + 2 & \text{if } x > k \text{ and } (k-1) \not \mid (x-k)\\ \frac{x-k}{k-1} + 1 & \text{if } x > k \text{ and } (k-1) \mid (x-k) \end{cases}$$

(3.1)

The above estimates of LUT requirements are based on the fact that LUTs are perhaps the most important and viable option for implementing combinational logic in FPGAs. Combinational logic blocks with higher number of inputs are expected to be implemented by a cascade of LUTs, with permitted amount of parallel processing, along the signal propagation path. However, for hardware-efficient implementations, the designer must explore the additional logical capabilities that the LUTs of modern day FPGAs provide. In addition, there are other hardware primitives available in the target FPGA platform to reduce the LUT requirement, such as the wide function multiplexers and the carry chains which must be considered for the purpose of implementation. The above closed form expression in (3.1) for estimating hardware resource requirements, therefore, has the following limitations:

- It assumes that all LUTs provide single outputs, whereas modern FPGAs from Xilinx provides dual-output LUTs that can significantly reduce hardware cost, provided the logic functions to be mapped satisfy certain criteria.

- It must be remembered that certain logic expressions can be factored appropriately to form subexpressions that can be realized using a combination of hardware primitives such as LUTs, wide function multiplexers and carry chains, thereby providing multiple outputs out of a single slice. The closed form expressions in (3.1) possibly hint at an approximate upper bound on the number of LUTs required.

- The number of LUTs occupied is not an accurate estimate of the area requirements, it is the number of slices spanned by the logic elements which give an accurate estimate of the total area required for logic realization.

The philosophy behind estimating the hardware resource requirement in terms of the number of LUTs used [4] may not reflect its actual implementation on hardware. For example, let us consider the Boolean logic functionality of an 8:1 multiplexer, which is essentially an 11-input 1-output combinational logic function.

3.2 Existing Work 21

$$f(s_2, s_1, s_0, a, b, c, d, e, f, g, h) = s_2' s_1' s_0' a + s_2' s_1' s_0 b + s_2' s_1 s_0' c + s_2' s_1 s_0 d + s_2 s_1' s_0' e + s_2 s_1' s_0 f + s_2 s_1 s_0' g + s_2 s_1 s_0 h$$

$$(3.2)$$

Going by (3.1), lut(x) = 2 for k = 6. This information indicates that the first six variables go as input to the first LUT and the remaining five variables along with the output of the first LUT go as input to the second LUT. However on examining (3.2) closely, it can be observed that there is no possible way to decompose it to the following form comprising of two functions  $f_1$  and  $f_2$  which could have actually realized it using two LUTs:

$$f(s_2, s_1, s_0, a, b, c, d, e, f, g, h) = f_2 \underbrace{(f_1(x_1, x_2, x_3, x_4, x_5, x_6), x_7, x_8, x_9, x_{10}, x_{11})}_{\text{implemented using 1 LUT}}$$

where  $x_i$  can be any one of the variables of the function f.

#### 3.3 Guidelines for High-Performance Realization

We list certain elementary but useful observations below, which should act as important guidelines for compact and high-performance realization of circuits on modern high-end FPGAs from Xilinx. These particular forms of the Boolean functions were chosen because they are relevant in the optimal realization of several arithmetic functions of interest on the Virtex-5 and Virtex-6 platform, as demonstrated later in this work.

1. A six-input LUT can implement any arbitrary combinational logic function f, having a maximum of six inputs and a single output.

$$y = f(x_1, ..., x_n)$$

where  $2 \le n \le 6$  (3.3)

2. A six-input LUT can implement any arbitrary five (or less)-input two-output function where each of the single-output functions may or may not have shared inputs. For example, consider two functions *g* and *h*, where

$$g = f(x_1, ..., x_n)$$

with  $X = \{x_1, ..., x_n\},$  (3.4)

$$h = f(y_1, ..., y_m)$$

with  $Y = \{y_1, ..., y_m\}$  (3.5)

Here, the sets X and Y are called the *support* [2] of the functions g and h. For packing g and h into a single LUT, any one of the conditions must be satisfied:

- $4 \le |X| + |Y| \le 5$ ; if  $X \cap Y = \emptyset$  (i.e., g and h are orthogonal)

- $2 \le |X| + |Y| \le 10$ ; if  $X \cap Y \ne \emptyset$

where |X| and |Y| are the cardinality of the sets X and Y.

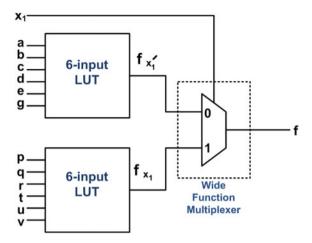

Fig. 3.1 Architecture mapping for Boolean logic that can be decomposed with respect to a single variable

3. Let f be a Boolean function of n variables ( $8 \le n \le 13$ ) which can be represented in the following form (see Fig. 3.1):

$$f(i_1, i_2, \dots, i_n) = x_1' f_{x_1'} + x_1 f_{x_1}$$

(3.6)

- Here,  $f_{x_1}$  and  $f_{x'_1}$  are each six (or less)-input combinational functions that can be individually realized using one LUT each.

- The wide function multiplexer present in the same slice as that of the LUTs computes the final expression, as shown in Fig. 3.1.

- Equation (3.1) however evaluates to lut(x) = 3, where  $x = x_{max} = 13$  (6 × 2 (two six-input LUTs) + 1 (select line)) and k = 6.

- If there exist p functions of the form as in f, the design requires  $\lceil p/2 \rceil$  slices, and 2p LUTs.

- An 8:1 multiplexer can be realized using this logic where the 6-input LUTs of Fig. 3.1 are configured as 4:1 multiplexers each (sharing the same select lines), and the wide function multiplexer selecting one of the LUT outputs.

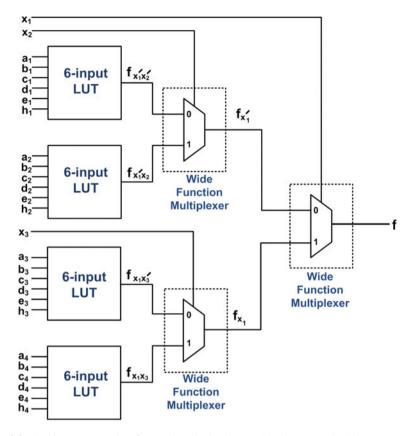

- 4. Let f be a function of n variables (17  $\leq n \leq$  26) such that we can apply recursive decomposition twice on it as shown below:

$$f(i_1, i_2, \dots, i_n) = x'_1 f_{x'_1} + x_1 f_{x_1}$$

$$= x'_1 (x'_2 f_{x'_1 x'_2} + x_2 f_{x'_1 x_2}) + x_1 (x'_3 f_{x_1 x'_3} + x_3 f_{x_1 x_3})$$

$$= x'_1 x'_2 f_{x'_1 x'_2} + x'_1 x_2 f_{x'_1 x_2} + x_1 x'_3 f_{x_1 x'_3} + x_1 x_3 f_{x_1 x_3}$$

(3.7)

- Here,  $f_{x'_1x'_2}$ ,  $f_{x'_1x_2}$ ,  $f_{x_1x'_3}$  and  $f_{x_1x_3}$  are each 6 (or less)-input combinational functions that can individually be realized using one LUT each.

- Three wide function multiplexers present in the same slice as that of the LUTs computes the final expression as shown in Fig. 3.2.

Fig. 3.2 Architecture mapping for Boolean logic that can be decomposed with respect to two variables

- Equation (3.1) however evaluates to lut(x) = 6, where  $x = x_{max} = 27$  (6 × 4 (four six-input LUTs) + 3 (select lines)) and k = 6.

- If there exists p functions of the form as in f, the design requires p slices and 4p LUTs.

- A 16:1 multiplexer can thus be mapped in a single slice using four LUTs, and three wide function multiplexers.

- 5. Consider any expression *R* of the following form:

$$R = a'b + a[X] \tag{3.8}$$

$$= a'b + a[c'd + c(Y)]$$

(3.9)

$$= a'b + a[c'd + c(e'f + e\{Z\})]$$

(3.10)

$$= a'b + a[c'd + c(e'f + e\{g'h + gi\})]$$

(3.11)

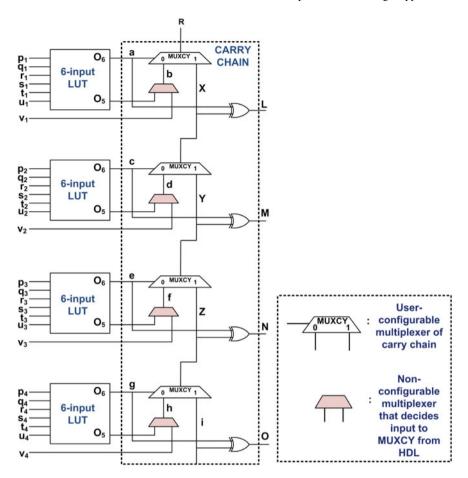

Fig. 3.3 Architecture mapping for Boolean logic that can exploit the carry chain

where X = c'd + cY, Y = e'f + eZ and Z = g'h + gi. Here i is a single input variable, and for every member of the pair (a, b), (c, d), (e, f), and (g, h), there can be either of the following possibilities:

- a. Both the members of the pair can individually be a maximum five (or less)-input function.

- b. First member can be a six (or less)-input function and second member can be a single variable function.

The above expression can be realized using four LUTs and a single carry chain, thereby occupying only a single slice in a modern high-end Xilinx FPGA, as shown in Fig. 3.3.

• The Boolean logic equation (3.11) essentially represents a cascade of 2:1 multiplexer functions.

- Here, R can have a maximum of 29 (6 × 4 (four six-input LUTs) + 4 inputs  $v_{4:1}$  external to the logic slice + 1 external input to the bottom MUXCY of the carry chain) input variables.

- If the Boolean logic function to be realized is of the form such that the variable i in (3.11) can be substituted by another expression bearing a similar resemblance to (3.11), and in such a way, if a total of n such substitutions can be carried out only at the position of variable i, then the entire expression can be realized using (n + 1) slices and a maximum of 4(n + 1) LUTs.

- From (3.1), we obtain lut(x) = 6, where x = 29 and k = 6 for which a minimum FPGA area of two slices are required. However, with the help of carry chain fabric, the entire architecture can be compacted within a single slice.

- A wide input AND and OR gate can be realized by the function R.

- Example of a wide (24-input) AND gate where the logic equation can be manipulated to fit the form of (3.11) as shown below:

$$R = a_{1}a_{2}a_{3}a_{4}a_{5}a_{6}a_{7}\cdots a_{18}a_{19}a_{20}a_{21}a_{22}a_{23}a_{24}$$

$$= \overline{a_{19}\cdots a_{24}}\cdot 0 + (a_{19}\cdots a_{24})[a_{18}a_{17}\cdots a_{1}a_{0}]$$

$$= \overline{a_{19}\cdots a_{24}}\cdot 0 + (a_{19}\cdots a_{24})[\overline{a_{13}\cdots a_{18}}\cdot 0 + (a_{13}\cdots a_{18})[a_{12}\cdots a_{0}]]$$

$$= \overline{a_{19}\cdots a_{24}}\cdot 0 + (a_{19}\cdots a_{24})[\overline{a_{13}\cdots a_{18}}\cdot 0 + (a_{13}\cdots a_{18})$$

$$[\overline{a_{7}\cdots a_{12}}\cdot 0 + (a_{7}\cdots a_{12})[\overline{a_{1}\cdots a_{6}}\cdot 0 + (a_{1}\cdots a_{6})\cdot 1)]]] \qquad (3.12)$$

Thus, going by Fig. 3.3,  $a = a_{19}a_{20}a_{21}a_{22}a_{23}a_{24}$ ,  $c = a_{13}a_{14}a_{15}a_{16}a_{17}a_{18}$ ,  $e = a_7a_8a_9a_{10}a_{11}a_{12}$  and  $g = a_1a_2a_3a_4a_5a_6$ , b = d = f = h = 0, and i = 1. Hence each 6-input LUT realizes a 6-input AND gate and the outputs of the 6-input LUTs are AND-ed using the carry chain.

• Example of a wide (24-input) OR gate where the logic equation can be manipulated to fit the form of (3.11) as shown below:

$$R = a_{1} + a_{2} + a_{3} + a_{4} + \dots + a_{21} + a_{22} + a_{23} + a_{24}$$

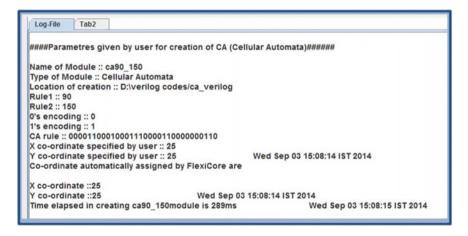

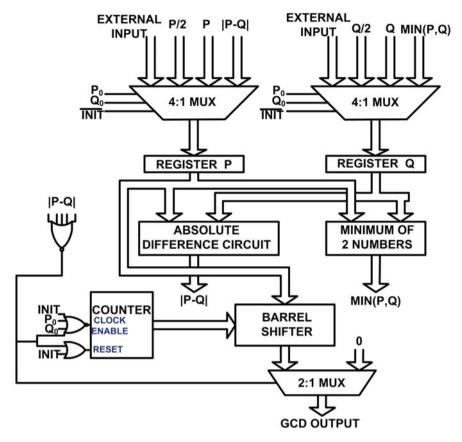

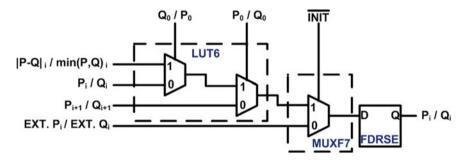

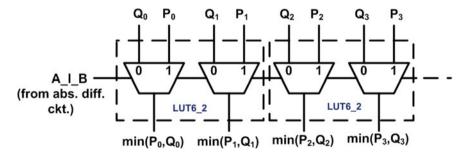

$$= (a_{19} + \dots + a_{24}) \cdot 1 + (\overline{a_{19} + \dots + a_{24}})[a_{18} + \dots + a_{1}]$$